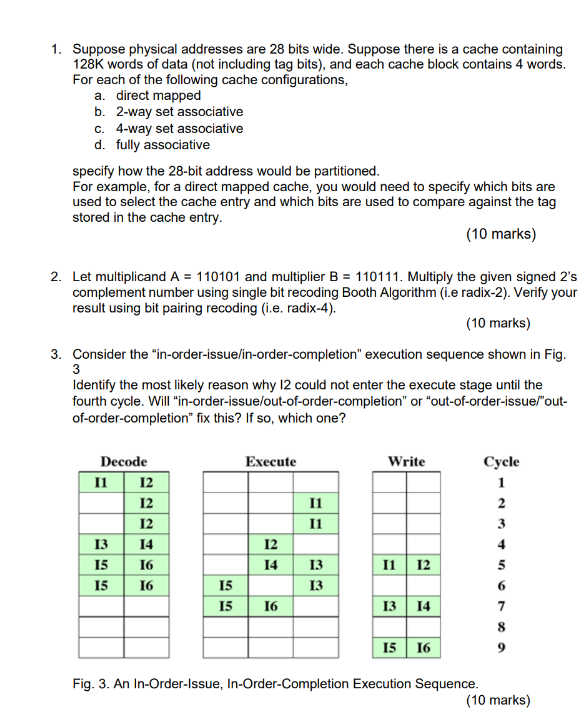

1. Suppose physical addresses are 28 bits wide. Suppose there is a cache containing 128K words of data (not including tag bits), and each cache block contains 4 words. For each of... 1. Suppose physical addresses are 28 bits wide. Suppose there is a cache containing 128K words of data (not including tag bits), and each cache block contains 4 words. For each of the following cache configurations, specify how the 28-bit address would be partitioned. a. direct mapped b. 2-way set associative c. 4-way set associative d. fully associative. 2. Let multiplicand A = 110101 and multiplier B = 110111. Multiply the given signed 2's complement number using single bit recoding Booth Algorithm (i.e., radix-2). Verify your result using bit pairing recoding (i.e., radix-4). 3. Consider the 'in-order-issue/in-order-completion' execution sequence shown in Fig. 3. Identify the most likely reason why I2 could not enter the execute stage until the fourth cycle. Will 'in-order-issue/out-of-order-completion' or 'out-of-order-issue/out-of-order-completion' fix this? If so, which one?

Understand the Problem

The questions require an analysis of cache configurations and an execution sequence, along with some multiplication tasks using Booth's algorithm. The first question is focused on memory architecture, the second on binary multiplication, and the third on execution sequencing in processors.

Answer

1.a: 9 tag, 15 index, 4 offset. 1.b: 10 tag, 14 index, 4 offset. 1.c: 11 tag, 13 index, 4 offset. 1.d: 24 tag, 0 index, 4 offset. 2: Result is -695. 3: Out-of-order execution can fix.

1.a: 9 tag bits, 15 index bits, 4 offset bits. 1.b: 10 tag bits, 14 index bits, 4 offset bits. 1.c: 11 tag bits, 13 index bits, 4 offset bits. 1.d: 24 tag bits, 0 index bits, 4 offset bits. 2: Result is -695. 3: Data hazard likely delayed I2; out-of-order execution can fix this.

Answer for screen readers

1.a: 9 tag bits, 15 index bits, 4 offset bits. 1.b: 10 tag bits, 14 index bits, 4 offset bits. 1.c: 11 tag bits, 13 index bits, 4 offset bits. 1.d: 24 tag bits, 0 index bits, 4 offset bits. 2: Result is -695. 3: Data hazard likely delayed I2; out-of-order execution can fix this.

More Information

For question 2, using Booth's algorithm (radix-2) simplifies multiplication of binary numbers by handling negative factors efficiently. In question 3, data hazards often prevent instructions from executing immediately.

Tips

Ensure correct calculation of the index and tag bits. For Booth's algorithm, carefully track and recode each step. Understand different cache configurations and their impacts.

Sources

AI-generated content may contain errors. Please verify critical information