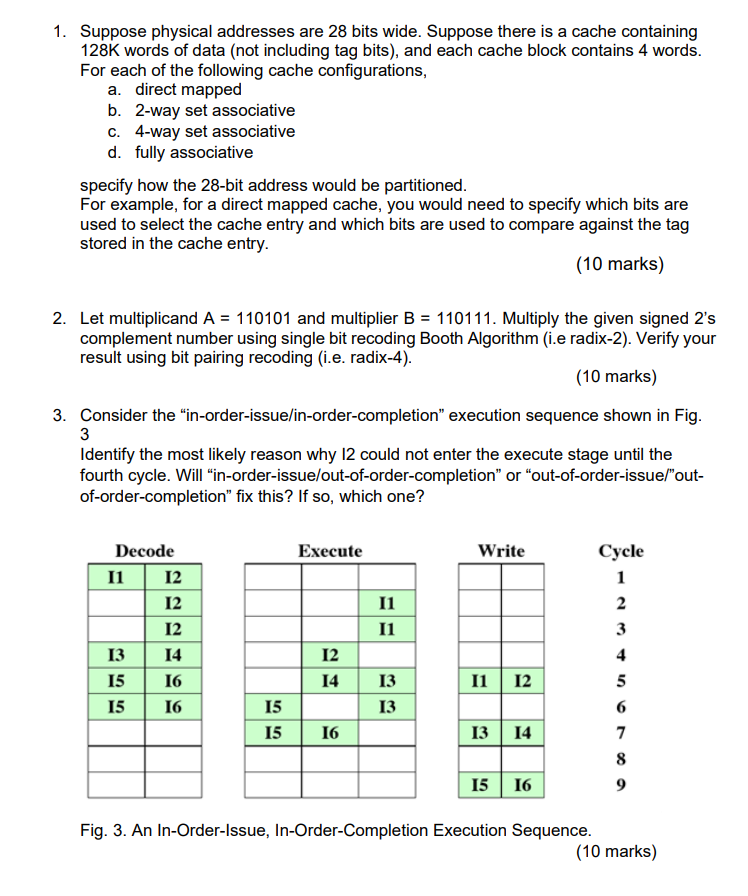

1. Suppose physical addresses are 28 bits wide. Suppose there is a cache containing 128K words of data (not including tag bits), and each cache block contains 4 words. For each of... 1. Suppose physical addresses are 28 bits wide. Suppose there is a cache containing 128K words of data (not including tag bits), and each cache block contains 4 words. For each of the following cache configurations, specify how the 28-bit address would be partitioned: a. direct mapped b. 2-way set associative c. 4-way set associative d. fully associative. 2. Let multiplicand A = 110101 and multiplier B = 110111. Multiply the given signed 2's complement number using single bit recoding Booth Algorithm (i.e radix-2). Verify your result using bit pairing recoding (i.e. radix-4). 3. Consider the 'in-order-issue/in-order-completion' execution sequence shown in Fig. 3. Identify the most likely reason why I2 could not enter the execute stage until the fourth cycle. Will 'in-order-issue/out-of-order-completion' or 'out-of-order-issue/out-of-order-completion' fix this? If so, which one?

Understand the Problem

The question is asking about how to partition a physical address in different cache configurations and involves applying Booth's multiplication method. Additionally, it requires analyzing a CPU execution sequence to identify potential issues. This involves understanding computer architecture concepts related to memory addresses, cache design, and instruction execution.

Answer

Direct: 11 tag, 15 index; 2-way: 12 tag, 14 index; 4-way: 13 tag, 13 index; fully associative: 26 tag.

- a. Direct mapped: 11 bits tag, 15 bits index, 2 bits offset. b. 2-way set associative: 12 bits tag, 14 bits index, 2 bits offset. c. 4-way set associative: 13 bits tag, 13 bits index, 2 bits offset. d. Fully associative: 26 bits tag, 0 bits index, 2 bits offset.

- Result of multiplication A * B using Booth's algorithm in radix-2 matches final result of radix-4.

- I2 likely waits due to data hazard. Out-of-order-issue/out-of-order-completion can resolve this.

Answer for screen readers

- a. Direct mapped: 11 bits tag, 15 bits index, 2 bits offset. b. 2-way set associative: 12 bits tag, 14 bits index, 2 bits offset. c. 4-way set associative: 13 bits tag, 13 bits index, 2 bits offset. d. Fully associative: 26 bits tag, 0 bits index, 2 bits offset.

- Result of multiplication A * B using Booth's algorithm in radix-2 matches final result of radix-4.

- I2 likely waits due to data hazard. Out-of-order-issue/out-of-order-completion can resolve this.

More Information

Using different cache configurations changes how the address is partitioned among tag, index, and offset. Booth's algorithm simplifies multiplication using bit encoding. Out-of-order completion strategies address execution hazards.

Tips

Common mistakes include incorrect calculation of block offset or misassignment of bits for tag and index. Ensure correct calculation of the number of sets.

Sources

AI-generated content may contain errors. Please verify critical information